Mi az ADC. Az ADC működésének általános elve DAC és ADC átalakító eszközök

Ez a cikk a különböző típusú ADC-k működési elvével kapcsolatos főbb kérdéseket tárgyalja. Ugyanakkor néhány fontos elméleti számítás az analóg-digitális konverzió matematikai leírásával kapcsolatban kimaradt a cikk keretein kívül, de hivatkozásokat adunk, ahol az érdeklődő olvasó mélyebb áttekintést kaphat az analóg-digitális átalakítás elméleti vonatkozásairól. az ADC működése. Így a cikk inkább az ADC-k általános működési elveinek megértésével foglalkozik, mint a működésük elméleti elemzésével.

Bevezetés

Kiindulásként definiáljuk az analóg-digitális átalakítást. Az analóg-digitális átalakítás egy bemeneti fizikai mennyiség numerikus reprezentációjává való átalakításának folyamata. Az analóg-digitális átalakító olyan eszköz, amely ilyen átalakítást végez. Formálisan az ADC bemeneti értéke bármilyen fizikai mennyiség lehet - feszültség, áram, ellenállás, kapacitás, impulzusismétlési sebesség, tengely forgási szöge stb. A pontosság kedvéért azonban a következőkben ADC alatt kizárólag feszültség-kód átalakítókat fogunk érteni.

Az analóg-digitális átalakítás fogalma szorosan összefügg a mérés fogalmával. Mérés alatt azt a folyamatot értjük, amikor a mért értéket összehasonlítjuk valamilyen szabvánnyal, analóg-digitális átalakításnál a bemeneti értéket valamilyen referenciaértékkel (általában referenciafeszültséggel) hasonlítjuk össze. Így az analóg-digitális átalakítás a bemeneti jel értékének méréseként is felfogható, és a metrológia összes fogalma, így például a mérési hibák is érvényesül rá.

Az ADC főbb jellemzői

Az ADC-nek számos jellemzője van, a főbbek a konverziós frekvencia és a bitmélység. A konverziós frekvenciát általában másodpercenkénti mintában (SPS) fejezik ki, a bitmélységet pedig bitben. A modern ADC-k bitszélessége akár 24 bit, konverziós sebessége pedig akár GSPS egység is lehet (természetesen nem egyszerre). Minél nagyobb a sebesség és a bitkapacitás, annál nehezebb elérni a kívánt jellemzőket, annál drágább és bonyolultabb a konverter. A konverziós sebesség és a bitmélység bizonyos módon összefügg egymással, és a sebesség feláldozásával növelhetjük a tényleges konverziós bitmélységet.

Az ADC-k típusai

Az ADC-knek sok típusa létezik, de ebben a cikkben csak a következő típusokra szorítkozunk:

- Párhuzamos konverziós ADC (közvetlen konverzió, flash ADC)

- Egymást követő közelítés ADC (SAR ADC)

- delta-sigma ADC (töltéskiegyensúlyozott ADC)

A közvetlen (párhuzamos) átalakítású ADC-k a legnagyobb sebességgel és a legkisebb bitmélységgel rendelkeznek. Például a Texas Instruments ADC TLC5540 párhuzamos konverziója 40MSPS sebességgel rendelkezik, mindössze 8 bittel. Az ilyen típusú ADC-k konverziós sebessége akár 1 GSPS is lehet. Itt megjegyezhető, hogy a csővezetékes ADC-k még nagyobb sebességgel rendelkeznek, de ezek több kisebb sebességű ADC kombinációja, és ezek figyelembevétele meghaladja jelen cikk kereteit.

A bitsebességű sorozat középső rését egymást követő közelítő ADC-k foglalják el. A tipikus értékek 12-18 bitesek, 100KSPS-1MSPS konverziós frekvenciával.

A legnagyobb pontosságot a sigma-delta ADC-k érik el, amelyek bitszélessége akár 24 bit is lehet, az SPS egységektől a KSPS egységekig terjedő sebességgel.

Az ADC egy másik típusa, amelyet a közelmúltban használtak, az integráló ADC. Az integráló ADC-ket mára szinte teljesen felváltották más típusú ADC-k, de a régebbi mérőműszerekben megtalálhatók.

Közvetlen konverziós ADC

A közvetlen konverziós ADC-k az 1960-as és 1970-es években terjedtek el, és az 1980-as években kezdték el gyártani integrált áramkörként. Gyakran használják a „pipeline” ADC-k részeként (a cikkben nem tárgyaljuk), kapacitásuk 6-8 bit, akár 1 GSPS sebességgel.

A közvetlen konverziós ADC architektúra az ábrán látható. 1

Rizs. 1. Közvetlen konverziós ADC blokkvázlata

Az ADC működési elve rendkívül egyszerű: a bemeneti jelet egyidejűleg a komparátorok összes „pozitív” bemenetére, a „negatív” bemenetekre pedig egy sor feszültséget táplálunk, amelyet a referenciafeszültségből kapunk ellenállásokkal osztva. R. Az ábra szerinti áramkörhöz. 1 ez a sor a következő lesz: (1/16, 3/16, 5/16, 7/16, 9/16, 11/16, 13/16) Uref, ahol az Uref az ADC referenciafeszültség.

Adjunk 1/2 Uref feszültséget az ADC bemenetre. Ekkor az első 4 komparátor fog működni (ha alulról számolunk), és a kimenetükön megjelennek a logikusak. A prioritási kódoló bináris kódot képez az egyesek „oszlopából”, amelyet a kimeneti regiszter rögzít.

Most egy ilyen konverter előnyei és hátrányai világosak. Minden komparátor párhuzamosan működik, az áramkör késleltetési ideje megegyezik az egyik komparátor késleltetési idejével plusz a kódoló késleltetési idejével. A komparátor és a kódoló nagyon gyorsan elkészíthető, így az egész áramkör nagyon nagy teljesítményű.

De N bit megszerzéséhez 2^N komparátorra van szükség (és a kódoló összetettsége is 2^N-nel nő). ábrán látható séma. 1. 8 komparátort tartalmaz és 3 bites, 8 bithez 256 komparátor kell, 10 bithez - 1024 komparátor, egy 24 bites ADC-hez több mint 16 millió. Ilyen magasságokat azonban még nem ért el a technológia.

egymás utáni közelítés ADC

Egy szekvenciális közelítési regiszter (SAR) analóg-digitális átalakító a bemeneti jel nagyságát szekvenciális „súlyozások” végrehajtásával méri, azaz a bemeneti feszültség értékének összehasonlítását a következőképpen generált értéksorozattal:

1. első lépésben a beépített digitális-analóg konverter kimenetét 1/2Uref értékre állítjuk (a továbbiakban feltételezzük, hogy a jel a (0 – Uref) intervallumban van.

2. Ha a jel nagyobb, mint ez az érték, akkor összehasonlítjuk a fennmaradó intervallum közepén lévő feszültséggel, azaz ebben az esetben 3/4Uref. Ha a jel kisebb, mint a beállított szint, akkor a következő összehasonlítás a hátralévő intervallum kevesebb mint felével történik (azaz 1/4Uref szinttel).

3. A 2. lépést N-szer megismételjük. Így N összehasonlítás („súlyozás”) N bitet eredményez az eredményből.

Rizs. 2. Egy egymást követő közelítési ADC blokkvázlata.

Így az egymást követő közelítő ADC a következő csomópontokból áll:

1. Összehasonlító. Összehasonlítja a „súlyozó” feszültség bemeneti értékét és aktuális értékét (a 2. ábrán háromszög jelzi).

2. Digitális-analóg konverter (DAC). A bemeneten kapott digitális kód alapján feszültség „súlyt” generál.

3. Successive Approximation Register (SAR). Egy egymást követő közelítő algoritmust valósít meg, generálva a DAC bemenetre betáplált kód aktuális értékét. A teljes ADC architektúra erről kapta a nevét.

4. Minta/Hold séma (Sample/Hold, S/H). Ennek az ADC-nek a működéséhez alapvetően fontos, hogy a bemeneti feszültség állandó maradjon az átalakítási ciklus során. A „valódi” jelek azonban idővel változnak. A minta- és tartási áramkör „emlékezik” az analóg jel aktuális értékére, és változatlan marad a készülék teljes működési ciklusa alatt.

Az eszköz előnye a viszonylag nagy konverziós sebesség: egy N bites ADC konverziós ideje N órajel. Az átalakítás pontosságát a belső DAC pontossága korlátozza, és 16-18 bites lehet (a 24 bites SAR ADC-k mostanra kezdtek megjelenni, például az AD7766 és AD7767).

Delta-Sigma ADC

Végül az ADC legérdekesebb típusa a szigma-delta ADC, amelyet a szakirodalom néha töltéskiegyensúlyozott ADC-nek nevez. A szigma-delta ADC blokkdiagramja az ábrán látható. 3.

3. ábra. A szigma-delta ADC blokkvázlata.

Ennek az ADC-nek a működési elve valamivel összetettebb, mint más típusú ADC-ké. Lényege, hogy a bemeneti feszültséget összehasonlítják az integrátor által felhalmozott feszültségértékkel. Az összehasonlítás eredményétől függően pozitív vagy negatív polaritású impulzusok kerülnek az integrátor bemenetére. Így ez az ADC egy egyszerű nyomkövető rendszer: az integrátor kimenetén lévő feszültség „követi” a bemeneti feszültséget (4. ábra). Ennek az áramkörnek az eredménye egy nullák és egyesek folyama a komparátor kimenetén, amelyet ezután egy digitális aluláteresztő szűrőn vezetnek át, ami N bites eredményt eredményez. LPF az ábrán. 3. „tizedelővel” kombinálva, olyan eszköz, amely a leolvasások gyakoriságát „tizedelve” csökkenti.

Rizs. 4. Sigma-delta ADC, mint nyomkövető rendszer

A pontosság kedvéért el kell mondanunk, hogy az ábrán. A 3. ábra egy elsőrendű szigma-delta ADC blokkvázlatát mutatja. A másodrendű sigma-delta ADC két integrátorral és két visszacsatoló hurokkal rendelkezik, de itt nem lesz szó róla. Akit érdekel ez a téma, tájékozódhat.

ábrán. Az 5. ábra az ADC-ben lévő jeleket mutatja nulla bemeneti szinten (felső) és Vref/2 szinten (alul).

Rizs. 5. Jelek az ADC-ben különböző bemeneti jelszinteken.

Most, anélkül, hogy bonyolult matematikai elemzésekbe merülnénk, próbáljuk megérteni, hogy a sigma-delta ADC-k zajszintje miért nagyon alacsony.

Tekintsük a szigma-delta modulátor blokkdiagramját, amely az ábrán látható. 3, és ebben a formában mutassa be (6. ábra):

Rizs. 6. Szigma-delta modulátor blokkvázlata

Itt a komparátort összeadóként ábrázoljuk, amely összeadja a folyamatos keresett jelet és a kvantálási zajt.

Legyen az integrátornak 1/s átviteli függvénye. Ezután a hasznos jelet X(s), a szigma-delta modulátor kimenetét Y(s)-ként, a kvantálási zajt pedig E(s)-ként ábrázolva megkapjuk az ADC átviteli függvényt:

Y(s) = X(s)/(s+1) + E(s)s/(s+1)

Valójában a szigma-delta modulátor egy aluláteresztő szűrő (1/(s+1)) a hasznos jelhez, és egy felüláteresztő szűrő (s/(s+1)) a zajhoz. azonos vágási frekvenciájú szűrők. A spektrum nagyfrekvenciás tartományában koncentrálódó zajt a modulátor után elhelyezett digitális aluláteresztő szűrő könnyedén eltávolítja.

Rizs. 7. A zaj „eltolódásának” jelensége a spektrum nagyfrekvenciás részébe

Azonban meg kell érteni, hogy ez egy rendkívül leegyszerűsített magyarázata a szigma-delta ADC zajalakításának jelenségére.

Tehát a sigma-delta ADC fő előnye a nagy pontosság, a saját zaj rendkívül alacsony szintje miatt. A nagy pontosság eléréséhez azonban szükséges, hogy a digitális szűrő vágási frekvenciája a lehető legalacsonyabb legyen, sokszorosa a szigma-delta modulátor működési frekvenciájának. Ezért a sigma-delta ADC-k konverziós sebessége alacsony.

Használhatók a hangtechnikában, de fő felhasználási területük az ipari automatizálás az érzékelőjelek átalakítására, a mérőműszerek és más olyan alkalmazások, ahol nagy pontosságra van szükség. de nincs szükség nagy sebességre.

Egy kis történelem

A történelem legrégebbi említése az ADC-ről valószínűleg Paul M. Rainey szabadalom, a "Facsimile Telegraph System", az Egyesült Államokban. 1 608 527 számú szabadalom, benyújtva 1921. július 20-án, kiadva 1926. november 30-án. A szabadalomban bemutatott eszköz valójában egy 5 bites közvetlen konverziós ADC.

Rizs. 8. Az ADC első szabadalma

Rizs. 9. Közvetlen konverziós ADC (1975)

Az ábrán látható eszköz a Computer Labs által gyártott, 1975-ben gyártott közvetlen konverziós ADC MOD-4100, amelyet diszkrét komparátorokkal szereltek össze. 16 komparátor van (félkörben helyezkednek el, hogy az egyes komparátorokhoz kiegyenlítsék a jelterjedési késleltetést), ezért az ADC mindössze 4 bites. Konverziós sebesség 100 MSPS, fogyasztás 14 watt.

Az alábbi ábra a közvetlen konverziós ADC továbbfejlesztett változatát mutatja.

Rizs. 10. Közvetlen konverziós ADC (1970)

A Computer Labs által gyártott 1970-es VHS-630 64 komparátort tartalmazott, 6 bites, 30MSPS volt, és 100 wattot fogyasztott (az 1975-ös verziójú VHS-675 75 MSPS-t és 130 wattot fogyasztott).

Irodalom

W. Kester. ADC Architectures I: A Flash Converter. Analog Devices, MT-020 oktatóanyag.

Mivel a digitális eszközök bemenetein lévő információk általában bináris kódban vannak ábrázolva, és a legtöbb automatizált folyamatvezérléshez használt aktuátor (működtetők, elektromágnesek és hasonlók) jellemzően a folyamatosan változó feszültség- vagy áramszintekre reagál, így az információt digitálisból analóg formába alakítja át. használt digitális-analóg átalakítók (DAC). A széles körű ipari alkalmazások mellett a DAC-okat a modern szórakoztatóelektronikában is használják, például fényalapú adathordozóra digitálisan rögzített, kiváló minőségű hangvisszaadó rendszerekben.

Az automatizált vezérlőrendszerekben a vezérelt ipari berendezések állapotával kapcsolatos információk megszerzéséhez különféle típusú nem elektromos mennyiségek átalakítóit (érzékelőket) használnak elektromos jelekké, amelyeket leggyakrabban analóg formában jelenítenek meg. Ezen információk digitális eszközökkel történő későbbi feldolgozásához az ilyen jeleket először digitális formába kell alakítani. A legáltalánosabb esetben az analóg-digitális átalakítás két szakaszban történik. Kezdetben a folyamatosan változó jelet diszkrét időpillanatokban lévő értékei helyettesítik, amit időmintavételezésnek nevezünk. Ezek a jelértékek ezután a bemenetre kerülnek analóg-digitális átalakítók (ADC), amelyek egy bizonyos szintű kvantálási lépéssel digitális megfelelőjével reprezentálják őket bináris kód formájában.

A DAC-k és ADC-k fő jellemzői a sebesség és a konverziós hiba, amelyet az abszolút konverziós hiba és a relatív felbontás határoz meg. A DAC és az ADC teljesítményét a konverziós idő jellemzi: a DAC esetében ez az az időtartam, amely a bemeneti bináris kód megérkezése után a kimeneti analóg jel létrehozásáig eltelik; egy ADC esetében a kezdetétől a kimeneti bináris kód vételéig eltelt idő.

Abszolút konverziós hiba szintről szintre egyenlő a kvantálás felével. Például egy kvantálási lépéssel egy n-bites DAC-nak különböző kimeneti feszültségértékeket kell biztosítania, amelyek maximális értékét az arányhoz tartozó skálafeszültségnek nevezik. ![]() . A relatív felbontás a lépésenkénti kvantálás és a skálafeszültség aránya. N-bites DAC-okhoz és ADC-khez.

. A relatív felbontás a lépésenkénti kvantálás és a skálafeszültség aránya. N-bites DAC-okhoz és ADC-khez.

Digitális-analóg átalakítók. A DAC-ok olyan eszközök, amelyek a bemenetén lévő bináris digitális kód számszerű megfelelőjének megfelelő feszültség (vagy áram) analóg kimeneti értékét állítják elő. A DAC kimeneti paraméterének, például a kimenetén lévő feszültségnek a függőségét a bemeneti jel kód megfelelőjétől konverziós karakterisztikának nevezzük. A 3.36a ábra egy négybites DAC konverziós jellemzőit mutatja.

A legegyszerűbb DAC működési elvét a 3.36b ábra diagramja szemlélteti. A DAC alapja a műveleti erősítő bemenetére bináris kóddal (például párhuzamos regiszterrel vagy számlálókóddal) vezérelt kapcsolókkal csatlakoztatott ellenállások mátrixa.

A , , és bemenetek átviteli együtthatói egyenlőek:

ahol azok a számok vannak, amelyek 0 és 1 értéket vesznek fel a megfelelő billentyűk helyzetétől függően.

A DAC kimeneti feszültségét a következő összeg határozza meg:

Így a négybites bináris kód 0-tól 15-ig terjedő szintre lesz konvertálva, ahol a kvantálási lépés. A kvantálási hiba csökkentése érdekében növelni kell a DAC bináris bitjeinek számát.

A DAC chipek sorozatszáma után az elsőnél a P betű (minden konverternél), a másodikon pedig az A betű. A 3.36c. ábrán egy K572PA1 típusú integrált áramkör látható, amely egy tízbites DAC-ból készült CMOS technológia alapján , legfeljebb 5 mikroszekundum konverziós idővel . Sajnos ennek az integrált áramkörnek a kifejlesztésekor technológiailag lehetetlen volt op-amp áramkört megvalósítani ugyanazon a hordozón a CMOS kapcsolókkal és az (R-2R) mátrixszal, így a K572PA1 DAC mindig kiegészül egy külső op-amp-mal. mikroáramkör, melynek bekötése a 3.36c ábrán is látható. Végezetül megjegyezzük, hogy a K572PA1 DAC egyedülálló lehetőséget biztosít egy analóg érték szorzására egy másik értékkel, amelyet bináris digitális kód határoz meg a D0-D9 bemeneteken, miközben a szorzás eredményét analóg formában is ábrázolja a DAC kimeneti feszültsége. Emiatt a K572PA1 DAC-ot néha szorzónak is nevezik.

Analóg-digitális átalakítók Az ADC-k egy digitális bináris kód és a bemeneti analóg jel szintjének összehasonlítására szolgáló eszköz. Az ADC konverziós karakterisztikája az ADC kimenetén lévő bináris kód numerikus megfelelőjének függése az analóg bemeneti feszültségtől. a jel normalizálva van rá. Ezt egy többlépcsős szaggatott vonal is ábrázolja, hasonlóan a 3.36a ábrán láthatóhoz, azzal az egyetlen különbséggel, hogy egy négybites ADC esetében az abszcissza és az ordináta tengely felcserélődik.

Jelenleg az integrált ADC-k legelterjedtebb osztályozása a bennük lévő konverziós folyamat időbeli fejlődésének jellegén alapul. E megközelítés szerint az összes integrált ADC három típusra osztható: szekvenciális (sweeping típusú) és párhuzamos (párhuzamos) cselekvésre. A sweeping típusú ADC-k közé tartoznak a szekvenciális számlálású ADC-k, bitenkénti kiegyenlítéssel (semmás közelítéssel) és integráló ADC-kkel.

A soros számláló ADC blokkvázlata a 3.37. ábrán látható. A komparátor üzemmódban működő DA1 op-amp nem invertáló bemenetére állandó (az olvasási impulzus időtartama alatt, amelynek időtartama a mintavételi periódusnál valamivel kisebbre van kiválasztva) pozitív feszültség kerül. A DA1 invertáló bemenetet a DAC DA2 kimeneti feszültsége táplálja (például egy lineárisan változó feszültségű generátorról), amelynek digitális bemenetei a CT2 bináris számláló kimeneteire vannak kötve. A CT2 számlálót a nullázási bemeneten lévő impulzus állítja a kezdeti nulla állapotba. Az ADC-t a „Start” bemeneten lévő impulzus váltja ki, amely lehetővé teszi a CT2 számláló működését, amelynek számláló bemenete ismétlési gyakorisággal kapja az óraimpulzusokat.

Analóg-digitális átalakítók (ADC) – ez egy olyan eszköz, amelynek segítségével egy bemeneti fizikai mennyiség numerikus ábrázolássá alakítása megy végbe. A bemeneti mennyiség lehet áram, feszültség, ellenállás, kapacitás.

Az ADC szorosan kapcsolódik a mérés fogalmához, amely a mért bemeneti mennyiség szabványával való összehasonlítási folyamatra vonatkozik. Vagyis az analóg-digitális átalakítás a bemeneti jel értékének mérése, és ennek megfelelően a mérési hiba fogalma alkalmazható rá.

Az ADC-nek számos jellemzője van, amelyek közül a legfontosabb a bitmélység és a konverziós frekvencia. A bitmélységet bitben, a konverziós frekvenciát pedig másodpercenkénti mintában fejezzük ki. Minél nagyobb a bit kapacitása és sebessége, annál nehezebb megszerezni a szükséges jellemzőket, és annál bonyolultabb és drágább a konverter.

Az ADC elve, az összetétel és a szerkezeti diagramok nagymértékben függenek az átalakítási módszertől.

Osztályozás

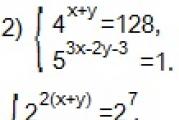

Jelenleg számos feszültség-kód átalakítási módszer ismert. Ezek a módszerek jelentősen eltérnek egymástól a lehetséges pontosságban, a konverziós sebességben és a hardver megvalósításának összetettségében. ábrán. A 2. ábra az ADC-k osztályozását mutatja be konverziós módszerek szerint.

Az analóg-digitális átalakítók típusai közül a legnépszerűbbek:

1. Párhuzamos konverziós ADC. Alacsony bitmélységgel és nagy teljesítménnyel rendelkeznek. A működés elve az, hogy a bemeneti jel a komparátorok „pozitív” bemeneteire kerül, a „negatív” bemenetekre pedig számos feszültség kerül. A komparátorok párhuzamosan működnek, az áramkör késleltetési ideje az egyik komparátor késleltetési idejének és a kódoló késleltetési idejének összege. Ez alapján a kódoló és a komparátor gyorssá tehető, és az áramkör nagy teljesítményt fog elérni.

2. Egymást követő közelítés ADC. Méri a bemeneti jel nagyságát a „súlyozások” sorozatával vagy a bemeneti feszültségértékek és számos érték összehasonlításával. Nagy konverziós sebesség jellemzi, és a belső DAC pontossága korlátozza.

3. ADC töltéskiegyenlítéssel. A működés elve a bemeneti feszültség összehasonlítása az integrátor által felhalmozott feszültségértékkel. Az impulzusok a negatív vagy pozitív polaritású integrátor bemenetére kerülnek az összehasonlítás eredménye alapján. Ennek eredményeként a kimeneti feszültség „követi” a bemeneti feszültséget. Nagy pontosság és alacsony zajszint jellemzi.

Az analóg-digitális átalakítást mindenhol használják, ahol analóg jelet kell digitális formában fogadni és feldolgozni.

- Az ADC a digitális voltmérő és multiméter szerves része.

- Speciális videó ADC-ket használnak a számítógépes TV-tunerekben, videobemeneti kártyákban és videokamerákban a videojelek digitalizálására. A számítógépek mikrofon- és vonali hangbemenetei audio-ADC-hez csatlakoznak.

- Az ADC-k az adatgyűjtő rendszerek szerves részét képezik.

- Az egychipes mikrokontrollerekbe 8-12 bites, egymást követő közelítésű ADC-ket és 16-24 bites szigma-delta ADC-ket építenek be.

- Nagyon gyors ADC-kre van szükség a digitális oszcilloszkópokban (párhuzamos és csővezetékes ADC-ket használnak)

- A modern mérlegek legfeljebb 24 bites felbontású ADC-ket használnak, amelyek közvetlenül a nyúlásmérő érzékelőből (sigma-delta ADC) alakítják át a jelet.

- Az ADC-k a rádiómodemek és más rádiós adatátviteli eszközök részét képezik, ahol a DSP processzorral együtt használják őket demodulátorként.

- Az ultragyors ADC-ket bázisállomás antennarendszerekben (az úgynevezett SMART antennákban) és radarantenna tömbökben használják.

34. Digitális-analóg átalakítók, célja, felépítése, működési elve.

Digitális-analóg átalakító (DAC) - digitális (általában bináris) kód analóg jellé (áram, feszültség vagy töltés) átalakítására szolgáló eszköz. A digitális-analóg átalakítók az interfészt jelentik a diszkrét digitális világ és az analóg jelek között.

Egy analóg-digitális átalakító (ADC) hajtja végre a fordított műveletet.

Az audio DAC általában impulzuskóddal modulált digitális jelet kap bemenetként. A különféle tömörített formátumok PCM-re konvertálásának feladatát a megfelelő kodekek látják el.

DAC alkalmazott amikor egy jelet digitális ábrázolásból analógra kell konvertálni, például CD-lejátszókban (Audio CD).

Négy csatornás analóg-digitális átalakító

Az elektromos jelek analóg-digitális átalakítása hasonló a terhelés mérlegen történő leméréséhez. Fibonacci olasz matematikus (1170-(1228-1250)) megfogalmazta a legkisebb súlyok problémáját a legnagyobb tartományú terheléseknél a karos mérlegen, amely a „súlyprobléma” néven vált ismertté. A probléma megoldása után Fibonacci arra a következtetésre jutott, hogy a legkisebb súlyszámot úgy kapjuk meg, ha a súlyok súlyait egy helyzetszimmetrikus hármas számrendszerben választjuk meg. Ebből következik, hogy a legoptimálisabb analóg-digitális átalakítók a helyzetszimmetrikus hármas számrendszerben működő analóg-digitális átalakítók. Ebből az is következik, hogy az „elektronikus mérés” messze elmarad a mechanikus mérlegeléstől, amelyben még a 12. században kialakult egy helyzetszimmetrikus hármas számrendszer. Az "elektronikus súlymérés" matematikája a 12. századi mechanikus mérlegelés matematikájának szintje alatt van. Azt is meg kell jegyezni, hogy Fibonacci problémájában nem vette figyelembe a mérlegelések számát. Ha figyelembe vesszük a mérlegelések számát (az iterációk száma az „elektronikus mérlegelésnél”), kiderül, hogy a legkevesebb mérés (iteráció) a helyzetszimmetrikus hármas számrendszer kiválasztásakor is előfordul.

Engedély

Az ADC felbontás az analóg jel nagyságának minimális változása, amelyet egy adott ADC átalakíthat. Általában voltban mérik, mivel a legtöbb ADC elektromos feszültséget használ bemeneti jelként. Egyetlen mérés esetén a zaj figyelembevétele nélkül a felbontás közvetlenül attól függ bit mélység ADC.

Az ADC kapacitása jellemzi, hogy a konverter hány diszkrét értéket tud előállítani a kimeneten. Bitekben mérve. Például egy 256 diszkrét érték (0..255) előállítására képes ADC szélessége 8 bit, mivel 2 8 = 256.

A feszültségfelbontás egyenlő a maximális és minimális kimeneti kódnak megfelelő feszültségek különbségével, osztva a kimeneti diszkrét értékek számával. Például:

- 1. példa

- Bemeneti tartomány = 0 és 10 volt között

- ADC kapacitása 12 bit: 2 12 = 4096 kvantálási szint

- Feszültségfelbontás: (10-0)/4096 = 0,00244 volt = 2,44 mV

- 2. példa

- Bemeneti tartomány = -10 és +10 volt között

- ADC kapacitása 14 bit: 2 14 = 16384 kvantálási szint

- Feszültségfelbontás: (10-(-10))/16384 = 20/16384 = 0,00122 volt = 1,22 mV

A gyakorlatban az ADC felbontását a bemeneti jel jel/zaj viszonya korlátozza. Ha az ADC bemenet zajintenzitása magas, a szomszédos bemeneti jelszintek megkülönböztetése lehetetlenné válik, vagyis romlik a felbontás. Ebben az esetben a ténylegesen elérhető felbontást a effektív bitmélység (effektív bitszám- ENOB), ami kisebb, mint az ADC tényleges bitkapacitása. Erősen zajos jel konvertálásakor a kimeneti kód alacsony rendű bitjei gyakorlatilag használhatatlanok, mivel zajt tartalmaznak. A deklarált bitmélység eléréséhez a bemeneti jel S/N arányának körülbelül 6 dB bitmélység bitenként kell lennie.

Konverziós típusok

Lineáris ADC-k

A legtöbb ADC lineárisnak tekinthető, bár az analóg-digitális átalakítás eleve nemlineáris folyamat (mivel a folytonos tér diszkrét térre való leképezésének művelete nemlineáris művelet). Term lineáris ADC-vel kapcsolatban azt jelenti, hogy a kimeneti digitális értékre leképezett bemeneti értékek tartománya lineárisan kapcsolódik ahhoz a kimeneti értékhez, azaz a kimeneti értékhez k-tól származó bemeneti érték tartományával érhető el

m(k + b) m(k + 1 + b),Ahol mÉs b- néhány állandó. Állandó b, általában értéke 0 vagy -0,5. Ha b= 0, az ADC-t hívják nem nulla fokozatú kvantáló (középső emelkedés), ha b= −0,5, akkor az ADC meghívásra kerül kvantáló nullával a kvantálási lépés közepén (középső futófelület).

Nemlineáris ADC-k

A nemlinearitást leíró fontos paraméter az integrál nemlinearitás(INL) és differenciális nemlinearitás(DNL).

Rekesznyílás hiba (remegés)

Digitalizáljunk egy szinuszos jelet x(t) = A sin2π f 0 t . Ideális esetben rendszeres időközönként leolvasásra kerül sor. A valóságban azonban a mintavétel időpontja ingadozásoknak van kitéve az órajel frontjának jittere miatt ( óra rezgés). Feltéve, hogy a mintavétel időpontjában a bizonytalanság Δ nagyságrendű t, azt találjuk, hogy a jelenség által okozott hiba a következőképpen becsülhető meg

Könnyen belátható, hogy alacsony frekvenciákon viszonylag kicsi a hiba, magas frekvenciákon viszont jelentősen megnőhet.

A rekesznyílás-hiba hatása figyelmen kívül hagyható, ha annak nagysága viszonylag kicsi a kvantálási hibához képest. Így a következő követelmények állíthatók be a szinkronizáló jel éli jitterére vonatkozóan:

Ahol q- ADC kapacitás.

| ADC kapacitás | Maximális bemeneti frekvencia | ||||

|---|---|---|---|---|---|

| 44,1 kHz | 192 kHz | 1 MHz | 10 MHz | 100 MHz | |

| 8 | 28,2 ns | 6,48 ns | 1,24 ns | 124 ps | 12,4 ps |

| 10 | 7,05 ns | 1,62 ns | 311 ps | 31,1 ps | 3,11 ps |

| 12 | 1,76 ns | 405 ps | 77,7 ps | 7,77 ps | 777 fs |

| 14 | 441 ps | 101 ps | 19,4 ps | 1,94 ps | 194 fs |

| 16 | 110 ps | 25,3 ps | 4,86 ps | 486 fs | 48,6 fs |

| 18 | 27,5 ps | 6,32 ps | 1,21 ps | 121 fs | 12,1 fs |

| 24 | 430 fs | 98,8 fs | 19,0 fs | 1,9 fs | 190 ac |

Ebből a táblázatból arra a következtetésre juthatunk, hogy célszerű egy bizonyos kapacitású ADC-t használni, figyelembe véve a szinkronizációs él jittere által támasztott korlátozásokat ( óra rezgés). Például értelmetlen precíziós 24 bites ADC-t használni hang rögzítésére, ha az óraelosztó rendszer nem tud ultraalacsony bizonytalanságot biztosítani.

Mintavételi gyakoriság

Az analóg jel az idő folyamatos függvénye, és az ADC-ben digitális értékek sorozatává alakul át. Ezért meg kell határozni azt a frekvenciát, amelyen a digitális értékek mintavételre kerülnek az analóg jelből. A digitális értékek előállításának gyakoriságát nevezzük mintavételi frekvencia ADC.

A folyamatosan változó, korlátozott spektrális sávú jel ki van téve digitalizálás(azaz a jelértékeket egy időintervallumban mérik T- mintavételi periódus) és az eredeti jel lehet pontosan diszkrét időértékekből interpolációval rekonstruálva. A rekonstrukció pontosságát a kvantálási hiba korlátozza. A Kotelnikov-Shannon-tétel szerint azonban a pontos rekonstrukció csak akkor lehetséges, ha a mintavételezési frekvencia nagyobb, mint a jelspektrum maximális frekvenciájának kétszerese.

Mivel a valódi ADC-k nem tudnak azonnal analóg-digitális átalakítást végrehajtani, az analóg bemeneti értéket állandónak kell tartani legalább az átalakítási folyamat elejétől a végéig (ezt az időintervallumot ún. konverziós idő). Ezt a problémát az ADC bemeneten lévő speciális áramkör - mintavételi és tartási eszköz - segítségével oldják meg. UVH. Az UVH általában egy kondenzátorban tárolja a bemeneti feszültséget, amely egy analóg kapcsolón keresztül kapcsolódik a bemenethez: amikor a kapcsoló zárva van, a bemeneti jel mintavételezésre kerül (a kondenzátor a bemeneti feszültségre töltődik), amikor kinyílik, tárolás történik. Számos integrált áramkör formájában készült ADC tartalmaz beépített digitális jelvezérlőt.

Aliasing

Minden ADC úgy működik, hogy meghatározott időközönként mintavételezi a bemeneti értékeket. Ezért a kimeneti értékek nem teljes képet adnak arról, hogy mi kerül be a bemenetbe. A kimeneti értékek alapján nem lehet meghatározni, hogyan viselkedett a bemeneti jel között minták. Ha tudja, hogy a bemeneti jel elég lassan változik a mintavételi frekvenciához képest, akkor feltételezheti, hogy a minták közötti közbenső értékek valahol ezeknek a mintáknak az értékei között vannak. Ha a bemeneti jel gyorsan változik, akkor nem lehet feltételezni a bemeneti jel közbenső értékeit, ezért nem lehet egyértelműen visszaállítani az eredeti jel alakját.

Ha az ADC által kibocsátott digitális értékek sorozatát valahol egy digitális-analóg konverter analóg formára alakítja vissza, kívánatos, hogy az így kapott analóg jel a lehető legpontosabb másolata legyen az eredeti jelnek. Ha a bemeneti jel megváltozik gyorsabban, mint a leolvasás, akkor a pontos jelrekonstrukció nem lehetséges, és hamis jel lesz jelen a DAC kimenetén. A jel hamis frekvenciájú komponenseit (az eredeti jel spektrumában nem található) hívják álnév(hamis frekvencia, hamis alacsony frekvenciájú komponens). Az aliasing sebesség a jelfrekvencia és a mintavételezési frekvencia különbségétől függ. Például egy 2 kHz-es, 1,5 kHz-es mintavételezésű szinuszhullám 500 Hz-es szinuszhullámként jeleníthető meg. Ezt a problémát az ún frekvencia aliasing (aliasing).

Az aliasing elkerülése érdekében az ADC bemenetre adott jelet egy aluláteresztő szűrőn kell átvezetni, hogy elnyomja azokat a spektrális komponenseket, amelyek frekvenciája meghaladja a mintavételi frekvencia felét. Ezt a szűrőt hívják élsimítás(anti-aliasing) szűrő, használata rendkívül fontos a valódi ADC-k építésekor.

Bár az aliasing a legtöbb esetben nemkívánatos hatás, jól használható. Ennek az effektusnak köszönhetően például elkerülhető a frekvencia lefelé történő konvertálása keskeny sávú nagyfrekvenciás jel digitalizálása során (lásd keverő). Ehhez azonban az ADC analóg bemeneti fokozatainak lényegesen magasabb paraméterekkel kell rendelkezniük, mint ami az ADC alap (videó vagy alacsony) harmonikus használatához szükséges.

Pszeudo-véletlen jel keverése (dither)

Egyes ADC jellemzők javíthatók pszeudo-véletlen jelkeverési technikával. remeg). Ez abból áll, hogy kis amplitúdójú véletlenszerű zajt (fehér zajt) adunk a bemeneti analóg jelhez. A zaj amplitúdója általában a minimális érték felének szintjén kerül kiválasztásra. Ennek az összeadásnak az a hatása, hogy az MZR állapot véletlenszerűen vált át a 0 és 1 állapotok között, nagyon kevés bemenettel (zaj hozzáadása nélkül az MZR hosszú ideig 0 vagy 1 állapotban lenne). Vegyes zajú jeleknél ahelyett, hogy egyszerűen a legközelebbi számjegyre kerekítené a jelet, véletlenszerű felfelé vagy lefelé kerekítés történik, és az átlagos időtartam, ameddig a jel egy adott szintre kerekítésre kerül, attól függ, hogy a jel milyen közel van ehhez a szinthez. . Így a digitalizált jel az MZR-nél jobb felbontású információt tartalmaz a jel amplitúdójáról, vagyis megnő az ADC effektív bitkapacitása. A technika negatív oldala a zaj növekedése a kimeneti jelben. Valójában a kvantálási hiba keneteket több szomszédos olvasat szerint. Ez a megközelítés kívánatosabb, mint a legközelebbi diszkrét szintre való egyszerű kerekítés. A pszeudo-véletlen jelek keverésének technikájának eredményeként a jel pontosabb időbeni reprodukálását kapjuk. A jel kis változásai az LSM pszeudo-véletlen ugrásaiból szűréssel visszaállíthatók. Ezen túlmenően, ha a zaj determinisztikus (a hozzáadott zaj amplitúdója bármikor pontosan ismert), akkor a digitalizált jelből kivonható úgy, hogy először növeli a bitmélységét, ezzel szinte teljesen megszabadulva a hozzáadott zajtól.

A nagyon kis amplitúdójú, pszeudo-véletlen jel nélkül digitalizált hangjeleket a fül nagyon torznak és kellemetlennek érzékeli. Pszeudo-véletlen jel keverésekor a valódi jelszintet több egymást követő minta átlagértéke reprezentálja.

A legtöbb ADC esetében a bitmélység 6 és 24 bit között van, a mintavételezési frekvencia pedig legfeljebb 1 MHz. Mega- és gigahertzes ADC-k is kaphatók (2002. február). Megahertz ADC-kre van szükség a digitális videokamerákban, videorögzítő eszközökben és digitális TV-tunerekben a teljes videojel digitalizálásához. A kereskedelmi forgalomban kapható ADC-k kimeneti hibája általában ±0,5–±1,5 LSB.

A mikroáramkörök költségét növelő egyik tényező a tűk száma, mivel ezek nagyobbra kényszerítik a chipcsomagot, és minden tűt a chiphez kell rögzíteni. A lábak számának csökkentése érdekében az alacsony mintavételezési frekvencián működő ADC-k gyakran rendelkeznek soros interfésszel. A soros interfésszel rendelkező ADC használata gyakran nagyobb csomagolási sűrűséget és kisebb kártyaterületet tesz lehetővé.

Az ADC chipek gyakran több analóg bemenettel rendelkeznek, amelyek egy analóg multiplexeren keresztül egyetlen ADC-hez vannak csatlakoztatva. A különféle ADC-modellek tartalmazhatnak minta- és tartási eszközöket, műszererősítőket vagy nagyfeszültségű differenciál bemenetet és más hasonló áramköröket.

Az ADC alkalmazása hangrögzítésben

Az ADC-ket a legtöbb modern hangrögzítő berendezésbe építik be, mivel a hangfeldolgozás általában számítógépeken történik; Még analóg felvétel használata esetén is szükség van egy ADC-re, hogy a jelet PCM adatfolyammá alakítsa, amelyet CD-re rögzítenek.

A hangrögzítéshez használt modern ADC-k akár 192 kHz-es mintavételezési frekvencián is működhetnek. Sokan ezen a területen úgy vélik, hogy ez a mutató redundáns, és pusztán marketing okokból használják (ezt bizonyítja a Kotelnyikov-Shannon tétel). Elmondható, hogy egy analóg audiojel nem tartalmaz annyi információt, amennyit egy digitális jel ilyen magas mintavételezési gyakoriság mellett tárolhat, és Hi-Fi (hardver osztályú) audioberendezéseknél gyakran 44,1 kHz (szabványos) mintavételi frekvenciát. CD-hez) vagy 48 kHz-et (a CD-hez szabványos) használunk. számítógépes hangreprezentációra jellemző). A széles sáv azonban leegyszerűsíti és csökkenti az élsimító szűrők megvalósításának költségeit, lehetővé téve, hogy kevesebb kapcsolattal vagy kisebb meredekséggel készüljenek a leállítósávban, ami pozitív hatással van a szűrő fázisválaszára az áteresztősávban.

A hangrögzítéshez használható analóg-digitális konverterek árának széles skálája van – 100 dollártól 10 000 dollárig vagy még több egy kétcsatornás ADC esetében.

A számítógépeken használt hangrögzítésre szolgáló ADC-k lehetnek belsőek vagy külsők. Van egy ingyenes PulseAudio szoftvercsomag Linuxhoz is, amely lehetővé teszi a kiegészítő számítógép(ek) használatát külső DAC/ADC-ként a fő számítógéphez, garantált késleltetéssel.

Egyéb alkalmazások

Az analóg-digitális átalakítást mindenhol használják, ahol egy jelet digitális formában kell feldolgozni, tárolni vagy továbbítani.

- A gyors videó ADC-ket például TV-tunerekben használják.

- A mikrokontrollerek gyakran tartalmaznak lassú, chipen lévő 8, 10, 12 vagy 16 bites ADC-ket.

- Nagyon gyors ADC-kre van szükség a digitális oszcilloszkópokban.

- A modern mérlegek legfeljebb 24 bites felbontású ADC-ket használnak, amelyek közvetlenül a nyúlásmérő érzékelőtől érkező jelet alakítják át.

- Az ADC-k a rádiómodemek és más rádiós adatátviteli eszközök részét képezik, ahol a DSP processzorral együtt használják őket demodulátorként.

- Az ultragyors ADC-ket bázisállomás antennarendszerekben (az úgynevezett SMART antennákban) és radarantenna tömbökben is használják.

Megjegyzések

Lásd még

Linkek

- Wolfgang Ries. Különböző típusú analóg-digitális konverterek tervezése és működési elve WBC GmbH Magazine “Components and Technologies” 2005. évi 3. szám

- Analóg-digitális átalakítók, elmélet és működési elvek a Microelectronics Market webhelyről

- Tanulás szimulációkkal A mintavételezési frekvencia és az ADC felbontás hatásait bemutató szimuláció.

- „Az analóg-digitális átalakító specifikációinak megértése” Len Staller cikke, 2005. február 24..

- A Flash ADC-k megismerése oktatóanyag a flash analóg-digitális konverterek (ADC) működéséről.

Irodalom

- Horowitz P., Hill W. Az áramkör-tervezés művészete. 3 kötetben: T. 2. Ford. angolról - 4. kiadás, átdolgozva. és további - M.: Mir, 1993. - 371 p. ISBN 5-03-002338-0.

- S. Norsworthy, R. Schreier, G. Temes, Delta-Sigma adatkonverterek. ISBN 0-7803-1045-4.

- Mingliang Liu, A kapcsolt kondenzátor áramkörök megfejtése. ISBN 0-7506-7907-7.

- Behzad Razavi. Az adatkonverziós rendszer tervezésének alapelvei. ISBN 0-7803-1093-4.

- David Jones, Ken Martin. Analóg integrált áramkör tervezés. ISBN 0-471-14448-7.

- Phillip E. Allen, Douglas R. Holberg. CMOS analóg áramkör tervezés. ISBN 0-19-511644-5.

- Hanzel G.E. Szűrőszámítási útmutató. USA, 1969. Ford. angolból, szerk. A. E. Znamenszkij. M.: „Szov. rádió", 1974. - 288 p. beteggel. UDC 621.372.541.061

3. sz. előadás

"Analóg-digitális és digitális-analóg átalakítás."

A mikroprocesszoros rendszerekben az impulzuselem szerepét egy analóg-digitális átalakító (ADC), az extrapolátor szerepét pedig egy digitális-analóg konverter (DAC) tölti be.

Analóg-digitális átalakítás az analóg jelben lévő információ digitális kóddá alakításából áll . Digitális-analóg átalakítás az inverz feladat végrehajtására készült, azaz. konvertálja a digitális kódként ábrázolt számot egyenértékű analóg jellé.

Az ADC-ket általában a digitális vezérlőrendszerek visszacsatoló áramköreibe telepítik, hogy az analóg visszacsatoló jeleket a rendszer digitális része által érzékelt kódokká alakítsák. Hogy. Az ADC-k számos funkciót látnak el, mint például: időmintavétel, szintkvantálás, kódolás. Az ADC általánosított blokkdiagramja a 3.1. ábrán látható.

Az ADC bemenetére áram vagy feszültség formájában jelet juttatnak, amelyet az átalakítási folyamat során szinttel kvantálnak. A 3 bites ADC ideális statikus karakterisztikáját a 3.2. ábra mutatja.

|

A bemeneti jelek bármilyen értéket felvehetnek a következő tartományban: Umaxtól Umaxig , és a kimenetek nyolc (2 3) diszkrét szintnek felelnek meg. Annak a bemeneti feszültségnek az értékét, amelynél az ADC kimeneti kód egyik értékéről egy másik szomszédos értékre átmenet történik, ún. interkód átmeneti feszültség. Az interkód átmenetek két szomszédos értéke közötti különbséget nevezzük kvantálási lépés vagy a legkisebb jelentőségű bit egysége (LSB).A transzformációs jellemzők kiindulópontja a bemeneti jel értéke által meghatározott pont, ként definiálva

(3.1),

ahol U 0,1 – az első interkód átmenet feszültsége, U LSB – kvantálási lépés ( LSB – Least Significant Bit ). átalakítása az összefüggés által meghatározott bemeneti feszültségnek felel meg

![]() (3.2).

(3.2).

Az ADC bemeneti feszültség tartománya korlátozott U 0,1 és U N-1,N hívott bemeneti feszültség tartomány.

(3.3).

Bemeneti feszültség tartomány és LSB érték N -bites ADC és DAC az arány szerint van összekötve

(3.4).

Feszültség

(3.5)

hívott teljes skálájú feszültség ( FSR – Teljes skálatartomány ). Ezt a paramétert általában az ADC-hez csatlakoztatott referencia feszültségforrás kimeneti szintje határozza meg. A kvantálási lépés nagysága vagy a legkisebb jelentőségű számjegy egysége, azaz. egyenlő

(3.6),

és a legjelentősebb számjegy mértékegységének értéke

![]() (3.7).

(3.7).

Amint a 3.2. ábrán látható, az átalakítási folyamat során olyan hiba lép fel, amely nem haladja meg a legkisebb jelentőségű bit értékének felét U LSB /2.

Különféle módszerek léteznek az analóg-digitális átalakításra, amelyek pontosságban és sebességben különböznek egymástól. A legtöbb esetben ezek a jellemzők antagonisztikusak egymással. Jelenleg az olyan típusú konverterek, mint az egymást követő közelítésű ADC-k (bitenkénti kiegyensúlyozás), integráló ADC-k, párhuzamos ( Vaku ) ADC, „sigma-delta” ADC stb.

Az egymást követő közelítés ADC blokkvázlata a 3.3. ábrán látható.

A készülék fő elemei egy komparátor (K), egy digitális-analóg konverter (DAC) és egy logikai vezérlő áramkör. A konverziós elv a bemeneti jel szintjének szekvenciális összehasonlításán alapul a kimeneti kód különböző kombinációinak megfelelő jelszintekkel, és az összehasonlítások eredményei alapján a kapott kód kialakításán. Az összehasonlított kódok sorrendje megfelel a felezés szabályának. Az átalakítás elején a DAC bemeneti kód olyan állapotba kerül, amelyben a legjelentősebb bitek kivételével minden bit 0, a legjelentősebb pedig 1. Ezzel a kombinációval a bemeneti feszültségtartomány felével egyenlő feszültség keletkezik a DAC kimenet. Ezt a feszültséget összehasonlítja a komparátor bemeneti feszültségével. Ha a bemeneti jel nagyobb, mint a DAC-ból érkező jel, akkor a kimeneti kód legjelentősebb bitje 1-re, ellenkező esetben 0-ra áll vissza. A következő órajelnél a részben így kialakított kód ismét a DAC bemenetén fogadva a következő bitet egyre állítjuk, és az összehasonlítás megismétlődik. A folyamat addig folytatódik, amíg a legkisebb jelentőségű bitet össze nem hasonlítjuk. Hogy. alkotnak N -bites kimeneti kód szükséges N azonos elemi összehasonlító ciklusok. Ez azt jelenti, hogy a többi tényező változatlansága mellett az ilyen ADC teljesítménye csökken a bitkapacitás növekedésével. Az egymást követő közelítő ADC belső elemeinek (DAC és komparátor) pontosságának jobbnak kell lennie, mint az ADC legkisebb szignifikáns bitjének fele.

A párhuzamos ( Vaku ) Az ADC a 3.4.

Ebben az esetben a bemeneti feszültséget az azonos nevű bemenetekkel való összehasonlítás érdekében azonnal tápláljuk N -1 összehasonlító. A komparátorok ellentétes bemeneteit egy nagy pontosságú feszültségosztó jelei látják el, amely referencia feszültségforráshoz van csatlakoztatva. Ebben az esetben az osztókimenetek feszültségei egyenletesen oszlanak el a bemeneti jel változásainak teljes tartományában. A prioritási kódoló a legmagasabb komparátornak megfelelő digitális kimeneti jelet állít elő aktivált kimeneti jel mellett. Hogy. szolgáltatni N -bit átalakítás szükséges 2 N osztó ellenállások és 2 N -1 összehasonlító. Ez az egyik leggyorsabb konverziós módszer. Nagy kapacitás esetén azonban nagy hardverköltségeket igényel. Az összes osztó és komparátor ellenállás pontosságának ismét jobbnak kell lennie, mint az LSB érték fele.

A kettős integrációs ADC blokkvázlata a 3.5. ábrán látható.

|

A rendszer fő elemei egy gombokból álló analóg kapcsoló SW 1, SW 2, SW 3. ábra, I integrátor, K komparátor és C számláló. Az átalakítási folyamat három fázisból áll (3.6. ábra).

|

Az első fázisban a kulcs zárva van S.W. 1, és a többi gomb nyitva van. Zárt kulcson keresztül S.W. Az 1. ábrán a bemeneti feszültséget egy integrátorra kapcsoljuk, amely integrálja a bemeneti jelet egy meghatározott időintervallumban. Ezen időintervallum után az integrátor kimeneti jelének szintje arányos a bemeneti jel értékével. Az átalakulás második szakaszában a kulcs S.W. 1 kinyílik és a kulcs S.W. A 2 bezárul, és a referencia feszültségforrásból jel érkezik az integrátor bemenetére. Az integráló kondenzátor az első konverziós intervallumban felhalmozott feszültségről a referenciafeszültséggel arányos állandó sebességgel kisüt. Ez a szakasz addig folytatódik, amíg az integrátor kimeneti feszültsége nullára nem esik, amint azt a komparátor kimenete jelzi, amely az integrátor jelét nullához hasonlítja. A második fokozat időtartama arányos az átalakító bemeneti feszültségével. A teljes második szakasz alatt kalibrált frekvenciájú nagyfrekvenciás impulzusokat küldenek a számlálóra. Hogy. a második fokozat után a digitális mérőállások arányosak a bemeneti feszültséggel. Ezzel a módszerrel nagyon jó pontosság érhető el anélkül, hogy magas követelményeket támasztanánk az alkatrészek pontosságával és stabilitásával szemben. Különösen az integrátor kapacitásának stabilitása lehet nem magas, mivel a töltési és kisütési ciklusok a kapacitással fordítottan arányos ütemben fordulnak elő. Ezenkívül a komparátor eltolódási és eltolási hibáit úgy kompenzálja, hogy minden átalakítási lépést ugyanazon a feszültségen indítanak és fejeznek be. A pontosság javítása érdekében az átalakítás harmadik szakaszát használják, amikor az integrátor kulcson keresztül visz be S.W. 3 nulla jelet adunk. Mivel ebben a lépésben ugyanazt az integrátort és komparátort használjuk, a nullánál lévő kimeneti hibaérték kivonása a következő mérésből kompenzálhatja a nullához közeli mérésekkel kapcsolatos hibákat. Még a pulthoz érkező órajelek frekvenciájára sem támasztanak szigorú követelményeket, mert az átalakítás első szakaszában rögzített időintervallumot képeznek ugyanazok az impulzusok. Szigorú követelmények csak a kisülési áramra vonatkoznak, pl. a referencia feszültségforráshoz. Ennek az átalakítási módszernek a hátránya az alacsony teljesítmény.

Az ADC-ket számos paraméter jellemzi, amelyek lehetővé teszik egy adott eszköz kiválasztását a rendszer követelményei alapján. Az összes ADC paraméter két csoportra osztható: statikus és dinamikus. Az előbbiek meghatározzák a készülék pontossági jellemzőit állandó vagy lassan változó bemeneti jellel történő munkavégzés esetén, az utóbbiak pedig úgy jellemzik a készülék teljesítményét, hogy a bemeneti jel frekvenciájának növekedésével a pontosságot megtartja.

A bemeneti jel nulla közelében lévő kvantálási szint –0,5 kódközi átmeneti feszültségnek felel meg U LSB és 0,5 U LSB (az első csak bipoláris bemeneti jel esetén fordul elő). A valós eszközökben azonban ezek az interkódolási átmeneti feszültségek eltérhetnek ezektől az ideális értékektől. Ezen interkód átmeneti feszültségek tényleges szintjének ideális értékétől való eltérését nevezzük bipoláris nulla eltolási hiba ( Bipoláris nulla hiba ) És unipoláris nullaponteltolás hiba ( Nulla offset hiba ) ill. A bipoláris konverziós tartományokhoz általában a nulla eltolási hibát, az unipoláris konverziós tartományokhoz pedig az unipoláris eltolási hibát használják. Ez a hiba a valós transzformációs karakterisztika párhuzamos eltolódásához vezet az ideális karakterisztikához képest az abszcissza tengely mentén (3.7. ábra).

|

Az utolsó interkód átmenetnek megfelelő bemeneti jelszint eltérése az ideális értékétől U FSR -1,5 U LSB , hívott teljes léptékű hiba ( Teljes léptékű hiba).

ADC konverziós arány a valós transzformációs karakterisztika kezdő- és végpontján keresztül húzott egyenes dőlésszögének érintőjének nevezzük. A konverziós együttható tényleges és ideális értéke közötti különbséget nevezzük konverziós tényező hibája ( Gain Error ) (3.7. ábra) Tartalmazza a skála végén lévő hibákat, de nem tartalmazza a skála nullánál lévő hibákat. Az unipoláris tartomány esetében a teljes skálahiba és az unipoláris nulla eltolási hiba különbségeként, a bipoláris tartomány esetében pedig a teljes skálahiba és a bipoláris nulla eltolási hiba közötti különbségként definiálható. Valójában mindenesetre ez az utolsó és az első interkód-átmenet közötti ideális távolság eltérése (egyenlő U FSR -2 U LSB ) valós értékétől.

A nullaponteltolás és az erősítési hibák az ADC előerősítő beállításával kompenzálhatók. Ehhez egy voltmérővel kell rendelkeznie, amelynek pontossága nem rosszabb, mint 0,1 U LSB . A két hiba függetlenségének biztosítása érdekében először a nulla eltolási hibát, majd az átalakítási együttható hibát javítsa ki.Az ADC nulla eltolási hibájának kijavításához a következőket kell tennie:

1. Állítsa be a bemeneti feszültséget pontosan 0,5-re U LSB;

2. Állítsa be az ADC előerősítő eltolását, amíg az ADC 00…01 állapotba nem vált.

A konverziós tényező hibájának kijavításához szükséges:

1. Állítsa be a bemeneti feszültséget pontosan a szintre U FSR -1,5 U LSB ;

2. Állítsa be az ADC előerősítő erősítését addig, amíg az ADC 11...1 állapotba nem vált.

Az ADC áramkör elemeinek tökéletlensége miatt az ADC karakterisztika különböző pontjain a lépések nagyságrendben különböznek egymástól és nem egyenlőek U LSB (3.8. ábra).

|

Két szomszédos valós kvantálási lépés felezőpontja közötti távolság eltérése a kvantálási lépés ideális értékétől U LSB hívott differenciális nemlinearitás (DNL – Differential Nonlinearity). Ha a DNL nagyobb vagy egyenlő U LSB , akkor az ADC-nek lehetnek úgynevezett „hiányzó kódjai” (3.3. ábra). Ez az ADC átviteli együttható helyi éles változását vonja maga után, ami a zárt hurkú vezérlőrendszerekben a stabilitás elvesztéséhez vezethet.

Azoknál az alkalmazásoknál, ahol fontos a kimeneti jel adott pontosságú fenntartása, fontos, hogy az ADC kimeneti kódok a lehető legpontosabban illeszkedjenek a kódok közötti átmeneti feszültségekhez. A valós ADC karakterisztika kvantálási lépésének középpontjának maximális eltérését a linearizált karakterisztikától ún. integrál nemlinearitás (INL – Integral Nonlinearity) illrelatív pontosság (Relatív pontosság) ADC (3.9. ábra).

|

A linearizált karakterisztikát a valós transzformációs karakterisztika szélső pontjain keresztül húzzuk át, miután azokat kalibráltuk, pl. A nulla eltolás és a konverziós tényező hibáit kiküszöböltük.

Szinte lehetetlen egyszerű eszközökkel kompenzálni a differenciális és integrál nemlinearitás hibáit.

ADC felbontás ( Felbontás ) az ADC kimeneten található kódkombinációk maximális számának reciproka

(3.8).

Ez a paraméter határozza meg, hogy az ADC milyen minimális bemeneti jelszintet érzékel (a teljes amplitúdójú jelhez viszonyítva).

A pontosság és a felbontás két független jellemző. A felbontás döntő szerepet játszik, ha fontos a bemeneti jel adott dinamikatartományának biztosítása. A pontosság akkor kritikus, ha a szabályozott változót egy adott szinten, rögzített pontossággal kell tartani.

Az ADC dinamikatartománya (DR – Dinamikus tartomány ) a maximális észlelt bemeneti feszültségszint és a minimum aránya, dB-ben kifejezve

![]() (3.9).

(3.9).

Ez a paraméter határozza meg, hogy az ADC mennyi információ maximális mennyiségét képes továbbítani. Tehát egy 12 bites ADC-hez DR = 72 dB.

A valódi ADC-k jellemzői eltérnek az ideális eszközök jellemzőitől a valódi eszköz nem ideális elemei miatt. Nézzünk meg néhány valódi ADC-t jellemző paramétert.

Jel-zaj arány(SNR – jel/zaj arány ) a bemeneti szinuszos jel effektív értékének a zaj effektív értékéhez viszonyított aránya, amely az összes többi spektrális komponens összege a mintavételi frekvencia feléig, az egyenáramú komponens nélkül. A tökéletesért N -bites ADC, amely csak kvantálási zajt generál SNR , decibelben kifejezve, így definiálható

(3.10),

(3.10),

ahol N – ADC bit kapacitás. Tehát egy 12 bites ideális ADC-hez SNR =74 dB. Ez az érték nagyobb, mint ugyanazon ADC dinamikus tartománya, mert Az észlelt jel minimális szintjének nagyobbnak kell lennie, mint a zajszint. Ez a képlet csak a kvantálási zajt veszi figyelembe, és nem veszi figyelembe a valódi ADC-kben létező egyéb zajforrásokat. Ezért az értékek SNR valódi ADC-k esetében általában alacsonyabb az ideálisnál. Tipikus érték SNR egy igazi 12 bites ADC-nél 68-70 dB.

Ha a bemeneti jelnek kisebb a kilengése U FSR , akkor az utolsó képletet módosítani kell

(3.11),

ahol KOS a bemeneti jel csillapítása, dB-ben kifejezve. Tehát, ha egy 12 bites ADC bemeneti jelének amplitúdója tízszer kisebb, mint a teljes skála feszültség fele, akkor KOS = -20 dB és SNR =74 dB – 20 dB = 54 dB.

Jelentése valódi SNR -ra használható fel az ADC bitek effektív számának meghatározása( ENOB – effektív bitszám ). A képlet határozza meg

![]() (3.12).

(3.12).

Ez a mutató jellemezheti egy valódi ADC tényleges döntő képességét, tehát egy 12 bites ADC, amelyre SNR =68 dB a KOS = -20 dB jelnél valójában 7 bites ( ENOB =7,68). ENOB érték erősen függ a bemeneti jel frekvenciájától, pl. Az ADC effektív bitkapacitása a frekvencia növekedésével csökken.

Teljes harmonikus torzítás ( THD – Teljes harmonikus torzítás ) az összes magasabb harmonikus négyzetgyökértékének és az alapharmonikus négyzetgyökértékének összegének aránya

(3.13),

(3.13),

ahol n általában 6-os vagy 9-es szinten korlátozott. Ez a paraméter az ADC kimeneti jelének a bemenethez viszonyított harmonikus torzítási szintjét jellemzi. THD a bemeneti jel frekvenciájával növekszik.

Teljes teljesítményű frekvenciasáv ( FPBW – Teljes teljesítmény sávszélesség ) a bemeneti jel maximális csúcstól csúcsig terjedő frekvenciája, amelynél a rekonstruált alapkomponens amplitúdója legfeljebb 3 dB-lel csökken. A bemeneti jel frekvenciájának növekedésével az ADC analóg áramköreinek már nincs idejük a változásait adott pontossággal feldolgozni, ami az ADC konverziós együtthatójának csökkenéséhez vezet magas frekvenciákon.

Letelepedési idő (Elszámolási idő ) az az idő, amely szükséges ahhoz, hogy az ADC elérje névleges pontosságát, miután a bemeneti jel teljes tartományával megegyező amplitúdójú léptetőjelet alkalmaztak a bemenetére. Ez a paraméter a különböző ADC csomópontok véges sebessége miatt korlátozott.

A különféle típusú hibák miatt a valódi ADC jellemzői nemlineárisak. Ha egy nemlinearitású eszköz bemenetére olyan jelet alkalmazunk, amelynek spektruma két harmonikusból áll f a és f b , akkor egy ilyen eszköz kimenőjelének spektrumában a főharmonikusokon kívül frekvenciájú intermodulációs szubharmonikusok is lesznek, ahol m, n =1,2,3,... Másodrendű szubharmonikusok f a + f b , f a - f b , a harmadrendű szubharmonikusok 2 f a + f b , 2 f a - f b , f a +2 f b , f a -2 f b . Ha a bemeneti szinuszosok hasonló frekvenciájúak, az áteresztősáv felső széle közelében helyezkednek el, akkor a másodrendű szubharmonikusok távol vannak a bemeneti szinuszoktól és az alsó frekvenciatartományban helyezkednek el, míg a harmadrendű szubharmonikusok frekvenciája közel van az áteresztősávhoz. bemeneti frekvenciák.

Intermodulációs torzítási tényező ( Intermodulatin torzítás ) az intermodulációs szubharmonikusok bizonyos nagyságrendű négyzetgyökértékeinek összegének az alapharmonikusok négyzetes középértékeinek összegének aránya, dB-ben kifejezve.

(3.14).

(3.14).

Bármely analóg-digitális átalakítási módszernek véges időre van szüksége. Alatt ADC konverziós idő ( Konverziós idő ) az analóg jel ADC bemenetre érkezésének pillanatától a megfelelő kimeneti kód megjelenéséig eltelt időintervallumra vonatkozik. Ha az ADC bemeneti jele idővel változik, akkor az ADC véges konverziós ideje az ún. rekesznyílás hiba(3.10. ábra).

|

A konverziós indítójel pillanatnyilag megérkezik t 0 , és a kimeneti kód pillanatnyilag megjelenik t 1 . Ezalatt a bemeneti jel mennyiségét sikerült megváltoztatniD U . Felmerül a bizonytalanság: a bemeneti jel értékének milyen szintje van a tartományban U 0 – U 0 + D U ennek a kimeneti kódnak felel meg. Ahhoz, hogy a konverziós pontosság a legkisebb szignifikáns bit egység szintjén megmaradjon, szükséges, hogy a konverziós idő alatt az ADC bemenetén a jel értékének változása ne legyen nagyobb, mint a legkisebbek egyikének az értéke. jelentős bit

![]() (3.15).

(3.15).

A jelszint változása az átalakítás során megközelítőleg a következőképpen számítható ki

(3.16),

(3.16),

ahol Uin - ADC bemeneti feszültség, Tc – konverziós idő. A (3.16)-ot (3.15)-re behelyettesítve kapjuk

![]() (3.17).

(3.17).

Ha a bemenet szinuszos jel frekvenciával f

![]() (3.18),

(3.18),

akkor a származéka egyenlő lesz

![]() (3.19).

(3.19).

Maximális értékét akkor veszi fel, ha a koszinusz egyenlő 1-gyel. Ezt figyelembe véve (3.9)-et (3.7)-re behelyettesítve azt kapjuk, hogy

![]() , vagy

, vagy

(3.20)

Az ADC véges konverziós ideje a bemeneti jel változási sebességének korlátozásához vezet. A rekesznyílási hiba csökkentése érdekében stb. az ADC bemeneti jel változási sebességének korlátjának gyengítésére az átalakító bemenetén, az ún. "mintavevő-tároló eszköz" (SSD) ( Track/Hold Unit ). Az UVH egyszerűsített diagramja a 3.11. ábrán látható.

|

Ennek az eszköznek két üzemmódja van: mintavételi mód és reteszelő üzemmód. A mintavételi mód a kulcs zárt állapotának felel meg S.W. . Ebben az üzemmódban az UVH kimeneti feszültsége megismétli a bemeneti feszültségét. A reteszelő módot a nyitógomb parancsa aktiválja S.W. . Ebben az esetben az UVH bemenete és kimenete közötti kapcsolat megszakad, és a kimenőjel a rögzítési parancs vételekori bemeneti jelszintjének megfelelő állandó szinten marad a készüléken felgyülemlett töltés miatt. kondenzátor. Így, ha közvetlenül az ADC konverzió megkezdése előtt ad ki egy tartási parancsot, az UVH kimeneti jele a teljes konverziós idő alatt állandó szinten marad. Az átalakítás befejezése után az UVH ismét mintavételi módba kapcsol. A valós UVH működése némileg eltér a leírt ideális esettől (3.12. ábra).

|

![]() (3.21),

(3.21),

ahol f - a bemeneti jel frekvenciája, t A – rekesznyílás-bizonytalanság értéke.

Valódi UVH-k esetén a kimeneti jel nem maradhat abszolút változatlan egy véges konverziós idő alatt. A kondenzátor fokozatosan kisül a kimeneti puffer kis bemeneti áramával. A szükséges pontosság fenntartásához szükséges, hogy az átalakítás során a kondenzátor töltése ne változzon 0,5-nél nagyobb mértékben U LSB.

Digitális-analóg átalakítók általában egy mikroprocesszoros rendszer kimenetére telepítik, hogy a kimeneti kódjait analóg jellé alakítsák át, amelyet egy folyamatos vezérlő objektumnak továbbítanak. A 3 bites DAC ideális statikus karakterisztikáját a 3.13. ábra mutatja.

|

Jellegzetes kiindulópont az első (nulla) bemeneti kódnak megfelelő pontként definiálva U 00…0 . Végpont jellemző az utolsó bemeneti kódnak megfelelő pontként definiálva U 11…1 . A kimeneti feszültség tartomány, a kvantáló egység legkisebb szignifikáns bitje, a nulla eltolási hiba és a konverziós együttható hiba meghatározása hasonló az ADC megfelelő jellemzőihez.

Szerkezeti felépítés szempontjából a DAC-k sokkal kevesebb lehetőséget kínálnak az átalakító felépítésére. A DAC fő szerkezete az ún. "lánc R -2 R diagram” (3.14. ábra).

Könnyen kimutatható, hogy az áramkör bemeneti árama az I in = U REF / R , és a lánc egymást követő láncszemeinek áramai rendreÉn a /2-ben, én a /4-ben, én benne /8 stb. A bemeneti digitális kód kimeneti árammá alakításához elegendő az átalakító kimeneti pontján összegyűjteni a bemeneti kódban szereplőknek megfelelő karok összes áramát (3.15. ábra).

|

Ha a konverter kimeneti pontjára műveleti erősítőt csatlakoztatunk, akkor a kimeneti feszültség a következőképpen határozható meg:

![]() (3.22),

(3.22),

ahol K - digitális kód bevitele, N – DAC bitmélység.

Az összes létező DAC két nagy csoportra osztható: az áramkimenettel és a feszültségkimenettel rendelkező DAC-okra. A köztük lévő különbség abban rejlik, hogy a DAC chipben nincs vagy van egy műveleti erősítő utolsó fokozata. A feszültségkimenettel rendelkező DAC-ok teljesebbek, és kevesebb kiegészítő alkatrészt igényelnek a működésükhöz. Az utolsó szakasz azonban az erdészeti áramkör paramétereivel együtt meghatározza a DAC dinamikai és pontossági paramétereit. Egy pontos, nagy sebességű műveleti erősítőt ugyanazon a chipen implementálni, mint egy DAC-t, gyakran nehéz. Ezért a legtöbb nagy sebességű DAC áramkimenettel rendelkezik.

Differenciális nemlinearitás a DAC esetében a kimenő analóg jel két szomszédos szintje közötti távolság eltérése az ideális értéktől. U LSB . A differenciális nemlinearitás nagy értéke a DAC nem monotonná válását okozhatja. Ez azt jelenti, hogy a digitális kód növekedése a kimeneti jel csökkenéséhez vezet a karakterisztika valamely részén (3.16. ábra). Ez nem kívánt generációhoz vezethet a rendszerben.

|

Integrál nemlinearitás DAC esetén, az analóg kimeneti jelszint legnagyobb eltéréseként definiálva az első és az utolsó kódnak megfelelő pontokon keresztül húzott egyenestől való egyenes vonaltól a beállításuk után.

Letelepedési idő A DAC az az idő, ameddig a DAC kimeneti jel egy adott szinten, legfeljebb 0,5 hibával létrejön. U LSB miután a bemeneti kód 00...0 értékről 11...1 értékre változott. Ha a DAC-nak vannak bemeneti regiszterei, akkor a beállási idő egy része a digitális jelek áthaladásának fix késleltetéséből adódik, és csak a fennmaradó része magának a DAC-áramkörnek a tehetetlensége. Ezért a beállási időt általában nem attól a pillanattól mérik, amikor új kód érkezik a DAC bemenetre, hanem attól a pillanattól kezdve, amikor a kimeneti jel elkezd változni, az új kódnak megfelelően, egészen addig, amíg a kimeneti jelet pontosan megállapítják. 0,5U LSB (3.17. ábra).

|

Ebben az esetben a beállási idő határozza meg a DAC maximális mintavételi frekvenciáját

(3.23),

hol t S – alapítási idő.

A DAC bemeneti digitális áramkörei véges sebességgel rendelkeznek. Ezenkívül a bemeneti kód különböző bitjeinek megfelelő jelek terjedési sebessége nem azonos az elemek és az áramköri jellemzők paramétereinek változása miatt. Ennek következtében a DAC létraáramkör karjai új kód érkezésekor nem szinkronban kapcsolnak, hanem egymáshoz képest némi késéssel. Ez oda vezet, hogy a DAC kimeneti feszültségének diagramján az egyik stacionárius értékről a másikra való átlépéskor különböző amplitúdójú és irányú túlfeszültségek figyelhetők meg (3.18. ábra).

|

|

A működési algoritmus szerint a DAC egy nulladrendű extrapolátor, melynek frekvenciaválasza a kifejezéssel reprezentálható.

(3.24),

(3.24),

Ahol w s - mintavételi gyakoriság. A DAC amplitúdó-frekvencia válaszát a 3.20. ábra mutatja.

|

Mint látható, 0,5-ös frekvenciánw s a rekonstruált jel 3,92 dB-lel csillapodik a jel alacsony frekvenciájú összetevőihez képest. Így a rekonstruált jel spektruma enyhén torzul. A legtöbb esetben ez a kis torzítás nem befolyásolja jelentősen a rendszer teljesítményét. Azonban azokban az esetekben, amikor a rendszer spektrális jellemzőinek megnövekedett linearitása szükséges (például hangfeldolgozó rendszerekben), a kapott spektrum kiegyenlítéséhez a DAC kimeneten, egy speciális visszaállító szűrőt kell telepíteni, amelynek frekvenciaválasza a típus x/sin(x).